4일 업계에 따르면 네패스는 최근 충북 괴산군 청안면 FO-PLP 공장 가동에 돌입했다.

글로벌 반도체 팹리스의 PMIC 제품을 FO-PLP로 양산하고 있다. 월 생산능력은 사각 패널 기준으로 1000장으로 알려졌다. 원형 웨이퍼 패키징으로 따지면 5000장 수준이다. 초도 물량이라 소규모지만 차세대 패키징 기술인 FO-PLP로 PMIC를 양산한 세계 최초 사례라 주목된다.

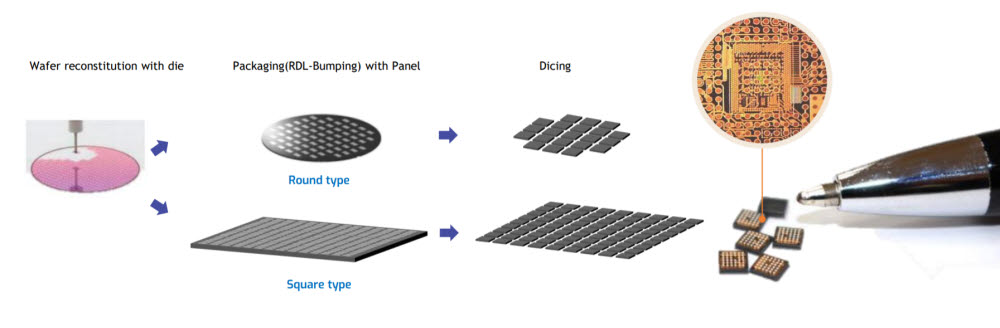

네패스가 양산 개시한 FO-PLP는 차세대 패키징 기술 중 하나다. 팬아웃(FO)은 반도체 입·출력 단자(I/O)를 칩 바깥으로 배치, I/O 수를 늘릴 수 있는 기술이다. 칩 전기적 성능과 열 효율성을 높이는 데 유리하다. 패널레벨패키징(PLP)은 사각형 패널 위에 칩과 기기를 직접 연결, 패키징하는 방식이다. 사각형이라 원형 대비 버리는 테두리를 최소화할 수 있다. 그만큼 많은 칩을 생산할 수 있다는 의미다. 이런 강점 덕분에 웨이퍼레벨패키징(WLP)보다 앞선 기술로 평가된다.

네패스가 청안 공장에 도입한 FO-PLP 공정은 600㎜ 정사각형 패널을 활용한다. 12인치(300㎜) 원형 웨이퍼 한 장 대비 약 5배 많은 칩(다이)을 생산할 수 있다. 고객사 입장에서는 PMIC의 높은 생산성을 확보, 시장 경쟁력을 갖출 수 있을 것으로 예상된다. 보통 PLP는 WLP 방식보다 생산성이 96% 높다고 평가 받는다.

-하 략-

권동준기자 djkwon@etnews.com

[원문보기 : 전자신문 https://www.etnews.com/20211004000023]