[시사저널e=고명훈 기자] 국내 반도체 후공정(OSAT) 전문기업 네패스가 반도체 2.5D 패키징 기술에 주력하며 반도체 크기를 줄일 수 있는 핵심 부품 기술을 개발했다. 네패스는 첨단 패키지 시장 선점을 가속한단 계획이다. 2.5D 패키징은 반도체 성능 향상과 발열 통제에 효과적이어서 인공지능(AI) 산업의 고도화에 따라 주목받는 패키징 기술이다.

22일 반도체업계에 따르면 네패스가 개발 중인 2.5D 패키징의 핵심 부품은 ‘재배선(RDL) 인터포저’다. 반도체 칩렛과 서브스트레이트(기판) 회로 사이에 추가로 들어가는 또 하나의 새로운 미세회로 기판으로, 중간에서 칩렛과 기판의 회로를 전기적으로 연결해주는 역할을 한다.

재배선 인터포저는 고분자 물질과 구리 배선으로 구성된 재배선 층으로 이뤄진다. 네패스는 재배선 층수에서 현재 일반적으로 쓰이는 6 레이어(Layer, 층) 외에도 업계 최초 8 레이어 기술을 개발 중이다. 기존의 6 레이어 구조에선 기판을 따로 사용해야 했다면, 8 레이어의 경우 기판 없이 패키징이 가능하므로 전체 패키지 크기를 줄일 수 있다. 또, 별도의 조립 과정을 거치지 않아도 돼 효율성이 높다.

강인수 네패스 반도체연구소장(전무)은 “RDL 층수에서 가장 일반적으로 알려진 것이 6 레이어인데 8 레이어까지 개발하고 있다”며 “레이어 수가 늘어났단 건 그라운드 레이어를 중간에 추가로 집어넣는 형태인데, 이러면 위층과 아래층의 배선 간 간섭을 없앨 수 있다”라고 설명했다.

그러면서 “현재 8 레이어를 하는 업체는 전 세계 어디에도 없는 것으로 안다”라고 부연했다.

재배선 인터포저는 기존 2.5D 구조 패키징에서 주로 쓰이던 실리콘(Si) 기반의 인터포저 대비 비용을 획기적으로 줄일 수 있단 장점을 지닌다. 두 제품의 가격 차이는 10분의 1 수준인 것으로 전해진다.

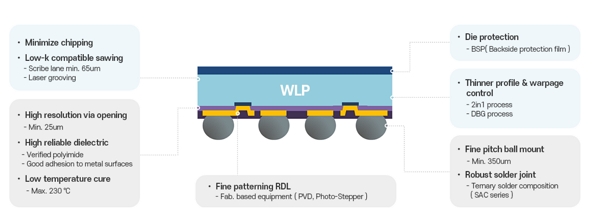

네패스가 재배선 인터포저 개발에 자신하는 이유는 웨이퍼레벨패키지(WLP) 분야에서 확보한 오랜 업력에 있다. WLP는 최종 가공을 마친 웨이퍼 상태에서 재배선, 범핑 공정 등을 하는 첨단 패키지 기술로, 패키지 크기를 줄이고 제조 비용을 절감할 수 있단 장점이 있다.

네패스는 양산 수준의 팬아웃(FO)-WLP 기술을 보유한 업체로 알려져 있다. 지난해 산업통상자원부가 발표한 ‘2023년 세계일류상품 및 생산기업’ 선정 수여식에서 회사의 WLP 기술이 ‘현재 세계일류상품’에 선정되기도 했다.

강 전무는 “현재 2.5D에 쓰이는 실리콘 소재의 인터포저는 좋긴 하지만 상당히 비싸서 미래에는 재배선 인터포저로 넘어가려는 추세”라며 “RDL 인터포저는 사실 WLP에서 나온 용어였고, TSMC도 CoWoS 패키지 기술에 실리콘 인터포저 대신 RDL 인터포저를 쓰겠다고 ‘CoWoS-R’이라고 이름을 붙인 것처럼 일반적으로 전 세계에서 많이 쓰는 제품”이라고 설명했다.

네패스는 내달 미국 콜로라도주 덴버에서 개최되는 ‘전자 부품 및 기술 컨퍼런스ECTC) 2024’에서 8 레이어 재배선 인터포저 기술 관련 발표할 계획이다. ECTC는 패키징, 전자 부품 등 영역에서 및 기술 교류의 장이 펼쳐지는 국제 권위의 행사로, 네패스는 FO와 WLP, 패널레벨패키지(PLP) 등 패키징 기술 세션에서 회사의 RDL 인터포저 관련 기술 개발 현황을 공유할 예정이다.

-하 략-

원문보기 https://www.sisajournal-e.com/news/articleView.html?idxno=402241