Leading the new era with

cutting-edge semiconductor packaging solution

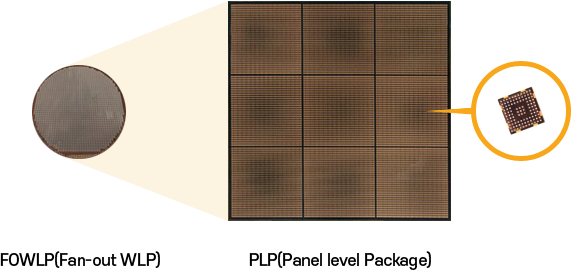

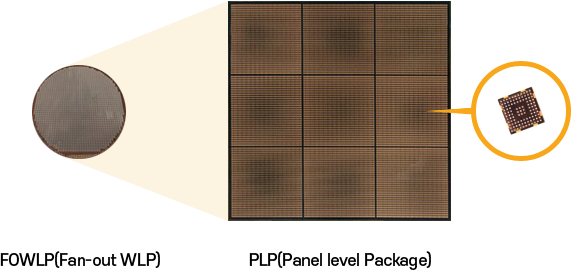

FOPLP

-

3D PoP Stackable( mPoP )

-

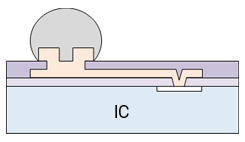

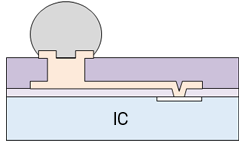

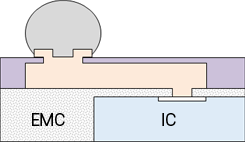

PoP( Package on Package )

-

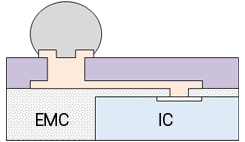

Multi-die( 2die )

-

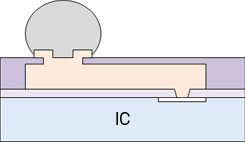

Chip-first( Face-up )

-

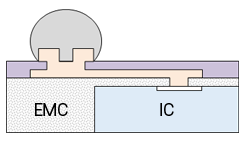

Chip-first( Face-down )

- 차세대 패키징 분야의 선도 기술

- 5G 및 클라우드 데이터 서버 등 4차 산업혁명에 필요한 고성능을 제공

- 대면적화된 사각패널 공정을 통해 팬아웃 웨이퍼레벨 공정 대비 생산성 증가 및 비용 절감 효과

- 발전된 팬아웃 패키징 기술(MCP, mPoP, PoP)는 PMIC, RF모듈, APE, 메모리 등과 같은 다양한 시장 및 제품에 적용 가능

2.5D RDL interposer

2.5D Chiplet

- 73μm, 45μm 피치, 25μm 직경의 u-bump 기술을 통해 높은 상호연결 밀도를 요구하는 차세대 반도체 패키징에 최적화

- 미세 피치 공정 기술(L/S 5/5μm 및 2/2μm)은 까다로운 레이아웃 요구 사항을 충족하는 정밀한 회로 설계 가능

- NPU와 HBM3 메모리를 통합한 고성능 모듈로 AI 및 고속 컴퓨팅 애플리케이션에 이상적인 탁월한 데이터 처리 성능 제공

2.5D Chiplet

- 고성능 AI 애플리케이션에 최적화된 핵심 기술로 차세대 컴퓨팅 역량 구현 가능

- 최대 처리 효율을 위해 AI 가속기와 고대역폭 메모리 통합 지원 설계

- 확장 가능하고 강력한 AI 시스템을 위한 미세 피치 및 고밀도 집적 기술 제공

FOWLP/WLP

-

[nWLPRB]

-

[nWLPHR]

-

[nWLPHC]

-

[FOWLP]

-

[FOWLP]

-

[FOWLP]

- 네패스만의 차별화된 기술로 고신뢰성, 고전류 WLP 솔루션 구현

- 첨단 IT 산업 외 Automotive, Areospace, Military 분야 제품에도 적용 가능