-

NEWS

NEWS

-

![[보도]안정호 네패스 부사장 “모두를 위한 AI 교육 환경 조성해야” [AI리더스 2025] - 조선일보 썸네일](https://www.nepes.co.kr/data/bbsData/17683767459.jpg) [보도]안정호 네패스 부사장 “모두를 위한 AI 교육 환경 조성해야” [AI리더스 2025] - 조선일보

[보도]안정호 네패스 부사장 “모두를 위한 AI 교육 환경 조성해야” [AI리더스 2025] - 조선일보안정호 네패스 디지털교육사업 총괄 부사장(CIO)은 최근 언론 인터뷰를 통해, 인공지능(AI) 시대에 공교육 현장이 기술 변화에 발맞춰 나가는 것이 중요하다고 밝혔다.네패스는 반도체 기술 기반의 역량을 교육 분야로 확장해, AI·디지털 교육 브랜드 코코아팹(kocoaFab)을 중심으로 맞춤형 학습 솔루션과 교육 콘텐츠를 개발·운영하고 있다. 이를 통해 학생 개개인의 학습 수준과 환경을 고려한 교육 프로그램을 제공하고, 교원 연수 및 공공 교육 사업에도 참여하고 있다.특히 음성 기반 AI 교구 등 접근성을 높인 기술을 통해 교육 소외계층까지 포용하는 AI 교육 환경 조성에 주력하고 있으며, 향후에는 국내에서 검증된 AI 교육 모델을 글로벌 확산 모델로 발전시키겠다는 계획도 밝혔다.안 부사장은 AI 교육의 핵심은 기술 자체가 아니라 이를 활용하는 사람과 교육 현장의 변화에 있다며, 모든 학생이 기술 격차 없이 AI 교육의 혜택을 누릴 수 있는 환경 조성에 지속적으로 힘쓰겠다는 의지를 전했다.원문 기사▶ 조선비즈안정호 네패스 부사장 “모두를 위한 AI 교육 환경 조성해야” (2025.12.31)원문 기사 바로가기

2026-01-14 -

네패스아크, 영남이공대와 반도체 테스트 분야 일학습병행 협약 체결

네패스아크, 영남이공대와 반도체 테스트 분야 일학습병행 협약 체결네패스아크는 이번 협약을 통해 교육과 채용을 유기적으로 연결하는 실질적 산학협력 모델을 구축하고, 반도체 산업 현장에서 요구하는 전문성과 실무 역량을 갖춘 인재 양성에 앞장설 예정이다.[사진=영남이공대 제공][보도자료 배포 리스트 추가 요청]

2025-12-19 -

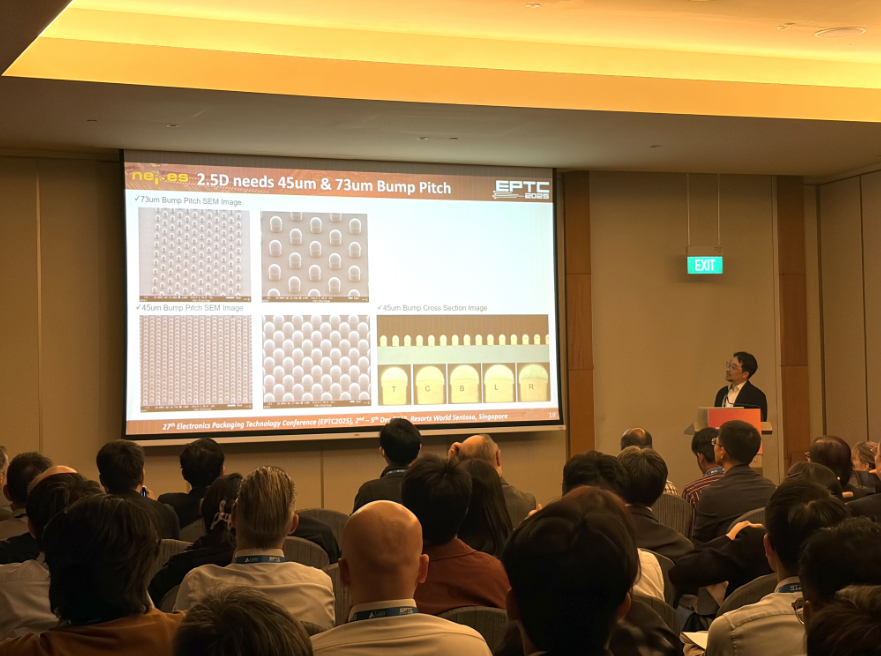

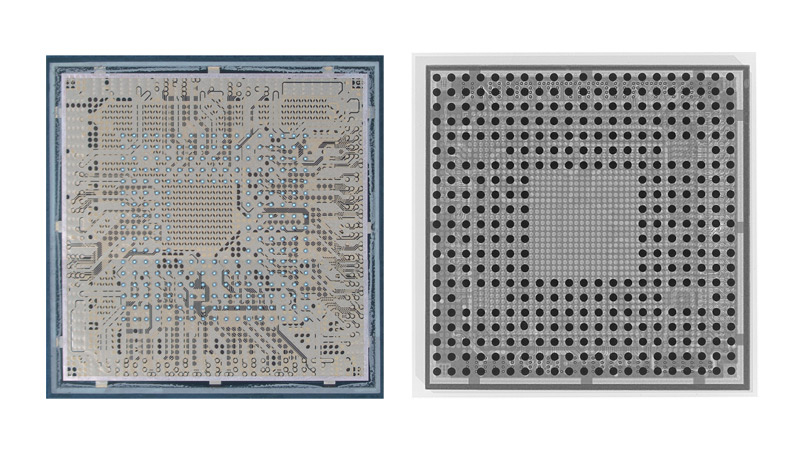

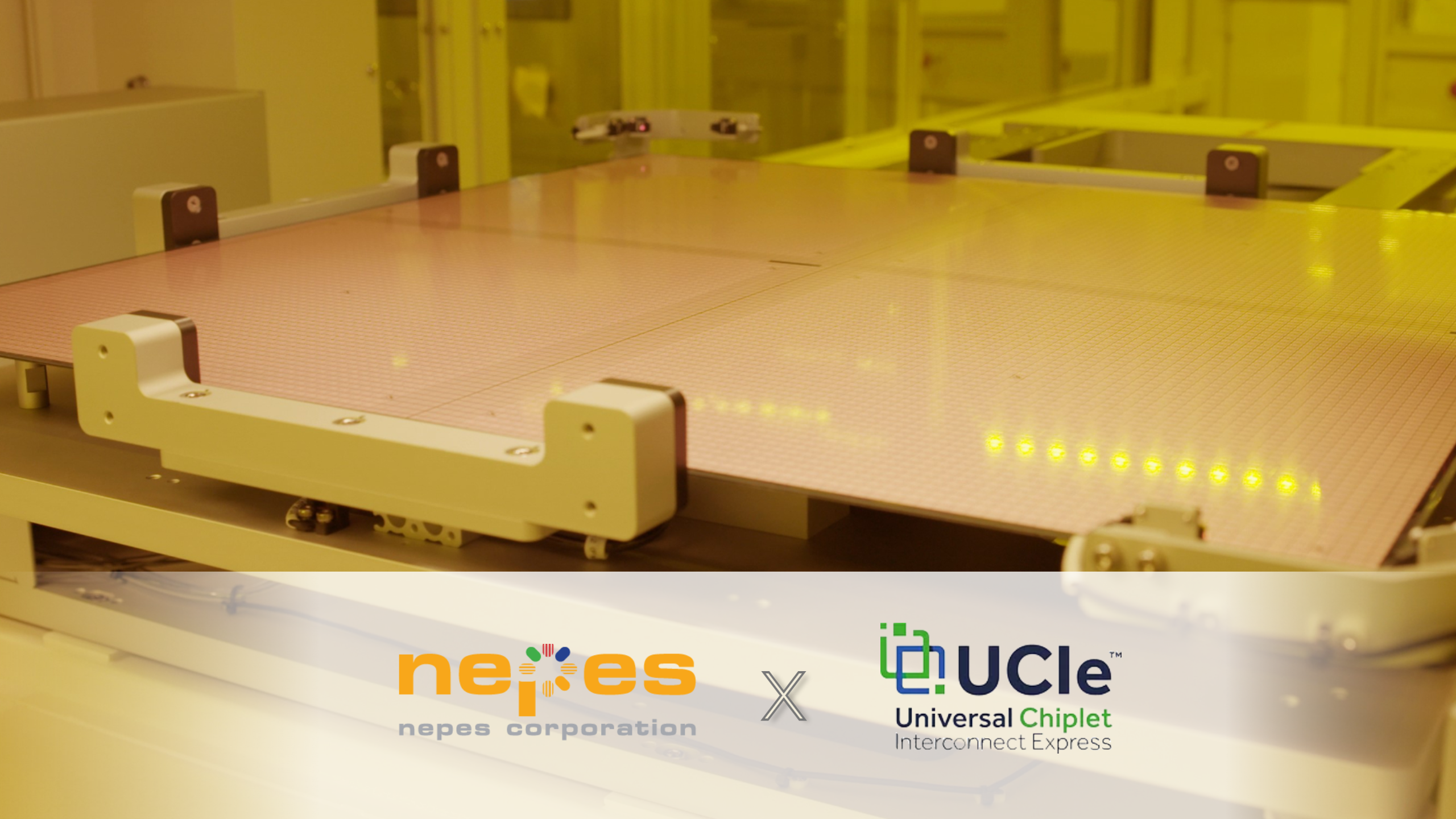

네패스, 글로벌 반도체 패키징 학회 EPTC 2025서 차세대 인터포저 기술 발표

네패스, 글로벌 반도체 패키징 학회 EPTC 2025서 차세대 인터포저 기술 발표네패스 반도체 연구소는 지난 12월 2일부터 5일까지 싱가포르에서 열린 IEEE Electronics Packaging Technology Conference(EPTC 2025)에 참가해, 「Development of Embedded Bridge Die Interposer Using Fan-out Packaging for Heterogeneous Integration of NPUs and HBMs」를 주제로 연구 성과를 발표했다.EPTC는 IEEE Electronics Packaging Society(EPS)가 주관하는 아시아·태평양 지역의 대표적인 반도체 패키징 및 이종집적 분야 국제 학회로, ASE, Amkor, TSMC, IMEC, A*STAR 등 글로벌 반도체 기업과 연구기관이 대거 참여해 최신 기술 동향을 공유하는 권위 있는 행사다. 이번 발표는 HPC·AI 시스템에서 NPU와 HBM을 단일 패키지 내에 고밀도로 집적해야 할 필요성이 커지는 가운데, 기존 실리콘 인터포저의 한계를 극복하기 위한 FOWLP(Fan-Out Wafer Level Packaging) 기반 Embedded Bridge Die 인터포저 기술을 소개한 것이다. 연구소는 자체 개발 중인 배선 형성 공정과 다이 본딩 공정 등 공정 흐름과 함께 개발 시제품을 공개하며 팬아웃 기술의 확장 가능성을 제시했다.이번 학회에서는 Hybrid Bonding을 포함한 Heterogeneous Integration 기술과 소재(Materials) 관련 발표가 주를 이루어 글로벌 연구·산업계의 기술 방향성을 확인했다. 이를 통해 네패스는 현재 개발 중인 2.5D 및 엣지 컴퓨팅 기술의 후속 공정 개발과 신뢰성 평가를 한층 강화할 필요성을 재확인했다고 밝혔다.[보도자료 배포 리스트 추가 요청]

2025-12-19 -

네패스 김태훈 사장, ‘제11회 중견기업인의 날’ 대통령 표창 수상

네패스 김태훈 사장, ‘제11회 중견기업인의 날’ 대통령 표창 수상네패스는 김태훈 사장(반도체사업총괄)이 12월 1일 서울 롯데호텔에서 개최된 ‘제11회 중견기업인의 날’ 기념식에서 대통령 표창을 수상했다고 밝혔다. 올해로 11회를 맞은 이번 행사에서는 김민석 국무총리, 문신학 산업통상부 제1차관, 최진식 한국중견기업연합회 회장을 비롯한 정·재계 주요 인사와 중견기업 대표 200여 명이 참석한 가운데, 대통령 표창을 포함한 총 57점의 정부 포상과 11점의 중견기업 성장탑이 수여됐다. 김태훈 사장은 삼성전자를 포함해 37년간 반도체 산업 전반에 걸쳐 전문성을 쌓아온 산업계 베테랑으로, 2016년부터 네패스 반도체사업을 총괄하며 기술 중심의 경영 혁신을 이끌고 있다.특히, 김 사장은 국내 최초로 600×600mm 패널레벨패키지(PLP)를 양산하고, CPB(Copper Pillar Bumping) 기술 기반의 AI 데이터센터용 전력반도체 시장 진입을 통해 글로벌 고객 발굴과 공급망 안정에 중추적 역할을 수행했다. 아울러, AI 제조혁신을 통한 경쟁력 강화, 정부 R&D 참여와 지식재산 확보, 그리고 매월 전 임직원과의 경영 소통 문화 정착을 이끄는 등 대한민국 반도체 산업 생태계와 지역경제 발전에 실질적인 기여를 한 점이 높은 평가를 받았다.한편, 네패스는 1990년 설립 이후 반도체 후공정 첨단 패키징과 전자재료 분야에서 전문성을 강화해 왔으며, 2022년에는 이병구 회장이 금탑산업훈장을 수훈한 데 이어 이번 대통령 표창으로 우수한 경영성과와 기술력을 다시 한 번 인정받았다.[보도자료 배포 리스트 추가 요청]

2025-12-02 -

네패스 - GIST, AI 반도체 첨단 패키징을 위한 업무협약(MOU) 체결

네패스 - GIST, AI 반도체 첨단 패키징을 위한 업무협약(MOU) 체결네패스는 광주과학기술원과 1일 GIST 행정동 대회의실에서 이종접합 첨단 패키징 경쟁력 강화를 위한 업무협약(MOU)을 체결했다.이번 협약은 GIST가 보유한 첨단 소재·공정·소자·회로 기반의 인공지능(AI) 반도체 연구 역량과 네패스의 반도체 첨단 패키징 기술 및 산업 노하우를 결합해 향후 온디바이스 AI 반도체 시대에 필수적인 이종접합 첨단 패키징 생태계를 구축하고 지역 반도체 산업 경쟁력을 강화하기 위해 마련했다.양 기관은 이번 협약을 바탕으로 GIST 첨단 AI 반도체 팹 센터내 연구 분소 설립을 추진하고, 공동 연구 및 인재 양성 프로그램을 확대하기로 했다.우선 첨단 AI 반도체 팹 센터 구축을 위한 중장기 전략과 정보 공유 체계를 마련해 반도체 산업 성장 기반을 강화한다. GIST의 연구 인프라와 네패스의 산업 전문성을 연계해 연구-교육-산업이 순환하는 협력 모델을 구축할 계획이다.또한 AI 반도체 경쟁력 강화를 위한 공동 연구개발(R&D)을 본격화하고, 기초 연구부터 산업화까지 연계되는 통합 연구 생태계를 조성한다. 교육·훈련 프로그램 공동 운영, 기술 교류 정례화, 산학 네트워크 확대 등을 추진해 전문 인력 양성과 연구 성과 확산을 이어갈 예정이다.1990년 케미컬 사업으로 출발한 네패스는 반도체·첨단소재·배터리 소재 등 국가 전략산업 전반에 사업 포트폴리오를 갖춘 중견 기업으로 성장했다. 최근에는 제조업 전반에 AI와 클라우드 기술을 접목하며 또 한 번의 혁신을 시도하고 있다.[보도자료 배포 리스트 추가 요청]

2025-12-01 -

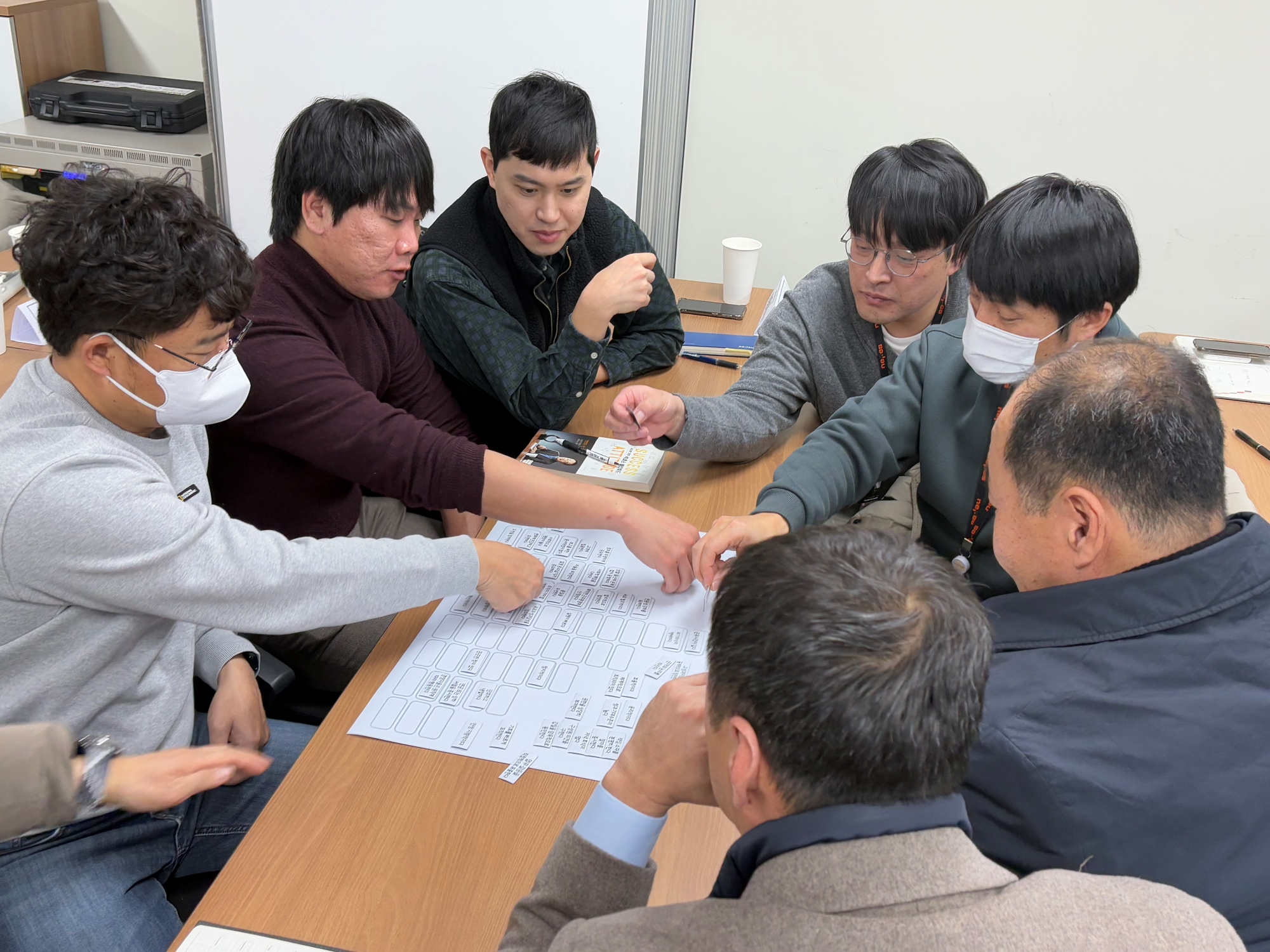

네패스, 2025 채용연계형 인턴 입문교육 성료

네패스, 2025 채용연계형 인턴 입문교육 성료네패스는 지난 11월 3일부터 7일까지 채용연계형 인턴을 대상으로 진행한 입문교육을 성공적으로 마쳤다고 밝혔다. 이번 교육에는 총 21명의 인턴이 참여했으며, 이들은 반도체사업부 전 부서에서 미래 핵심 인재로 성장할 준비를 시작했다.이번 입문교육은 조직의 비전과 핵심가치 내재화, AI 기반 실무 역량 강화, 핵심 직무 이해를 목표로 체계적으로 기획·운영되었다. 특히, Organizational Fit × AI-Driven × Skill-Up이라는 세 가지 축을 중심으로 설계되어 인턴들이 네패스의 문화에 빠르게 적응하고, 현업에서 요구되는 역량을 조기에 확보할 수 있도록 지원했다.교육 과정은 ▲네패스 기업문화 및 비전 이해 ▲AI 및 반도체 산업 트렌드 학습 ▲법정 필수 환경안전교육 ▲핵심 직무 아카데미(기술·품질·통합운영관리) 등으로 구성되었으며, 이후 3주간의 심화 직무 아카데미를 통해 실무 적용 능력을 강화할 예정이다.교육생들은 전반적으로 높은 만족도를 보였으며, 적극적인 참여와 소통을 통해 자기주도적 성장 의지를 보여주었다. 또한, 현업 적용을 위한 구체적인 실천 계획을 다수 도출하며, 향후 정규직 전환을 위한 기반을 마련했다.네패스 관계자는 “이번 입문교육은 단순한 지식 전달을 넘어, 네패스의 미래를 이끌어갈 인재들이 조직의 일원으로 성장할 수 있는 토대를 마련한 의미 있는 과정”이라며, “앞으로도 인턴들이 네패스에서 원활히 정착하고 역량을 발휘할 수 있도록 적극 지원할 것”이라고 말했다.[보도자료 배포 리스트 추가 요청]

2025-11-19 -

네패스, 대한민국인공지능혁신대상 ‘부문대상’ 수상

네패스, 대한민국인공지능혁신대상 ‘부문대상’ 수상AI 기반 공교육 혁신과 디지털 포용 실천으로 교육 생태계 선도㈜네패스가 11월 10일 열린 2025 대한민국인공지능혁신대상에서 AI 교육 혁신 부문 대상을 수상했다. 이번 행사는 대한민국 인공지능혁신대상위원회가 주최하고, 국제미래학회·전자신문·국회미래정책연구회·대한민국 인공지능포럼이 공동주관하며, 과학기술정보통신부·산업통상자원부 등 정부 주요 부처가 후원하는 국내 대표 AI 시상식이다. ‘K-AI 휴머니즘과 혁신’을 주제로, AI 기술을 통한 산업 혁신과 사회적 가치 실현에 기여한 기업과 기관을 포상한다.네패스는 지난 10여 년간 AI·디지털 기술을 접목한 교육 혁신을 선도하며, 인간 중심의 교육철학을 바탕으로 대한민국 AI 교육 생태계 조성에 기여해왔다.네패스는 2013년부터 ▲AI 교육 제품 및 콘텐츠 개발 ▲인간-AI 협력 교육모델 연구 ▲정부 공교육 사업 수행 ▲교육 소외계층 대상 AI 교육 등 다양한 활동을 통해 매년 12만 명 이상의 학생과 교사에게 AI 교육을 제공해왔다.특히, 기술기업 아이오테드와 함께 ChatGPT 기반 음성인식 AI 교육용 스피커 ‘AI 금쪽이’를 개발하여 초등학생 및 특수학생의 문제해결 역량을 키우는 데 기여했으며, 서울대학교와의 협업을 통해 인간-AI 협력 교육모델을 학술적으로 검증하고 실증 연구를 진행했다.또한, 네패스는 생성형 AI 기반 학습 플랫폼을 통해 개인 맞춤형 교육을 실현하고, 현직 교사 5,600여명이 참여하는 학습 커뮤니티 ‘코코아팹 스쿨’을 운영하며 교육 현장의 디지털 전환을 이끌고 있다.공교육 혁신뿐 아니라, 네패스는 AI 윤리 교육 콘텐츠 개발, 사회 문제 해결 중심의 PBL 프로그램 ‘Digital Hero’ 운영, 도서벽지·다문화가정 등 교육 소외계층 대상 CSR 활동을 통해 공공성과 사회적 책임을 실천하고 있다.네패스 관계자는 “AI 중심의 미래를 현실로 만드는 반도체 패키징 혁신 기업으로서, 교육 분야에서도 AI 기술을 통해 더 나은 사회를 만드는 데 앞장서겠다”고 밝혔다.이번 수상은 네패스가 기술 혁신을 넘어 교육 격차 해소와 디지털 포용, 윤리적 AI 활용이라는 사회적 가치 실현에 기여한 점을 높이 평가받은 결과다.[보도자료 배포 리스트 추가 요청]

2025-11-13 -

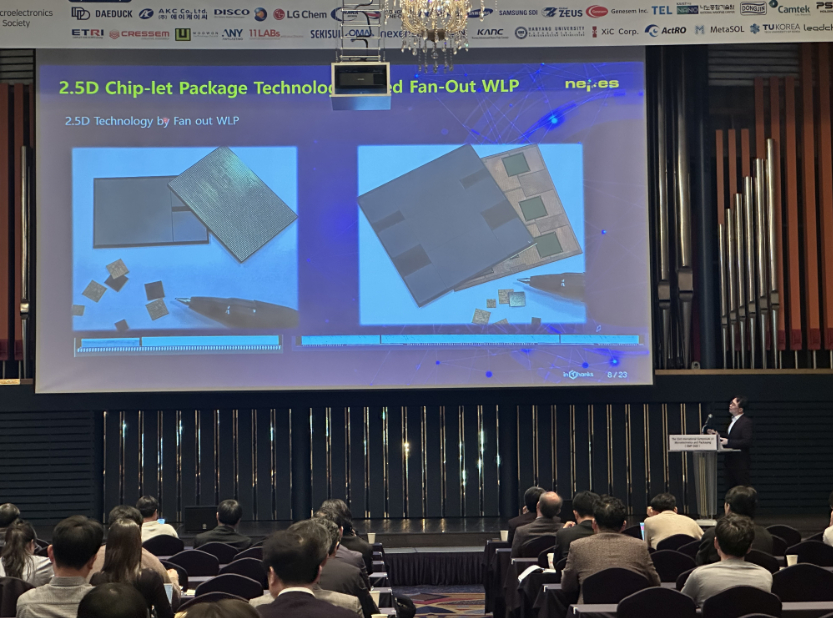

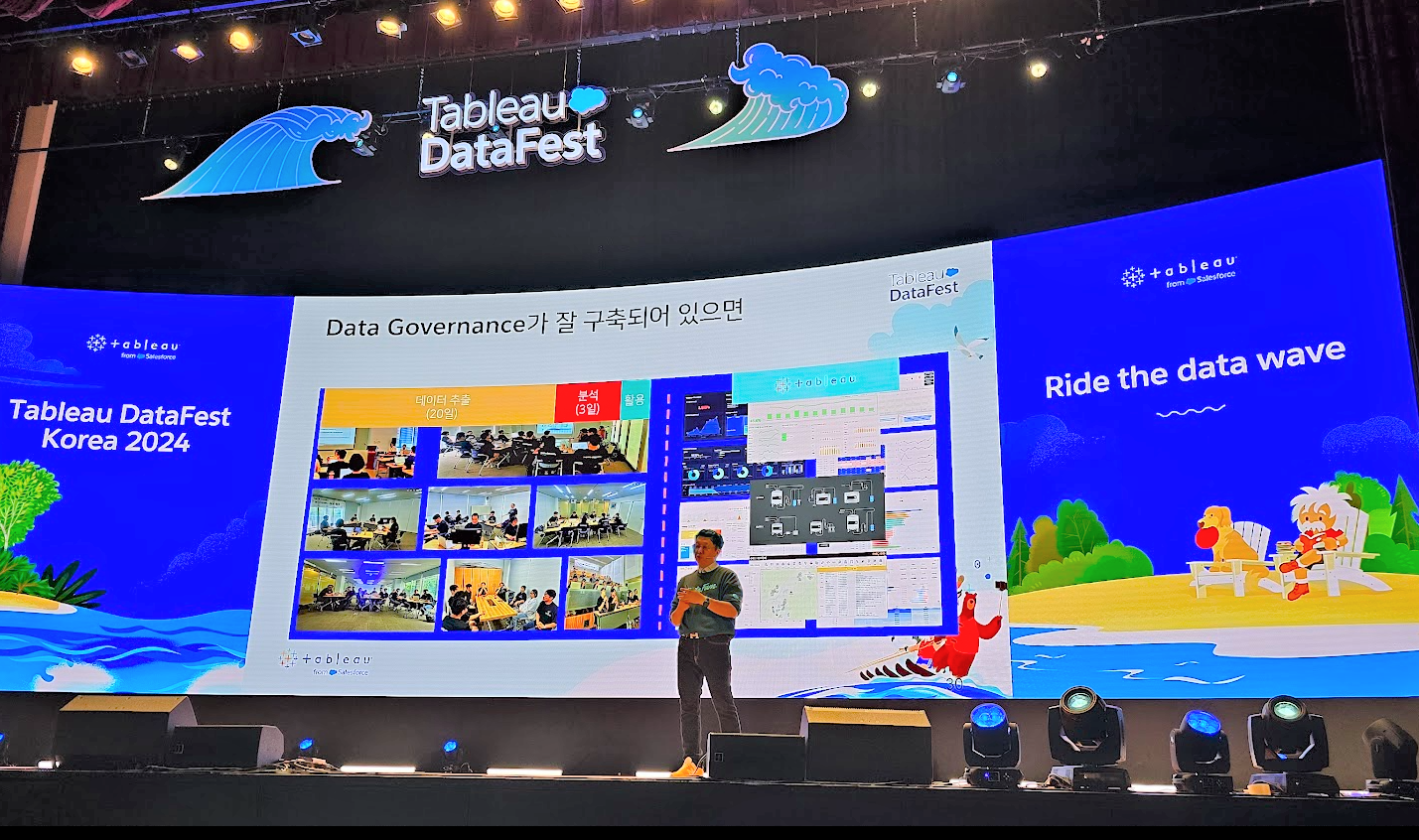

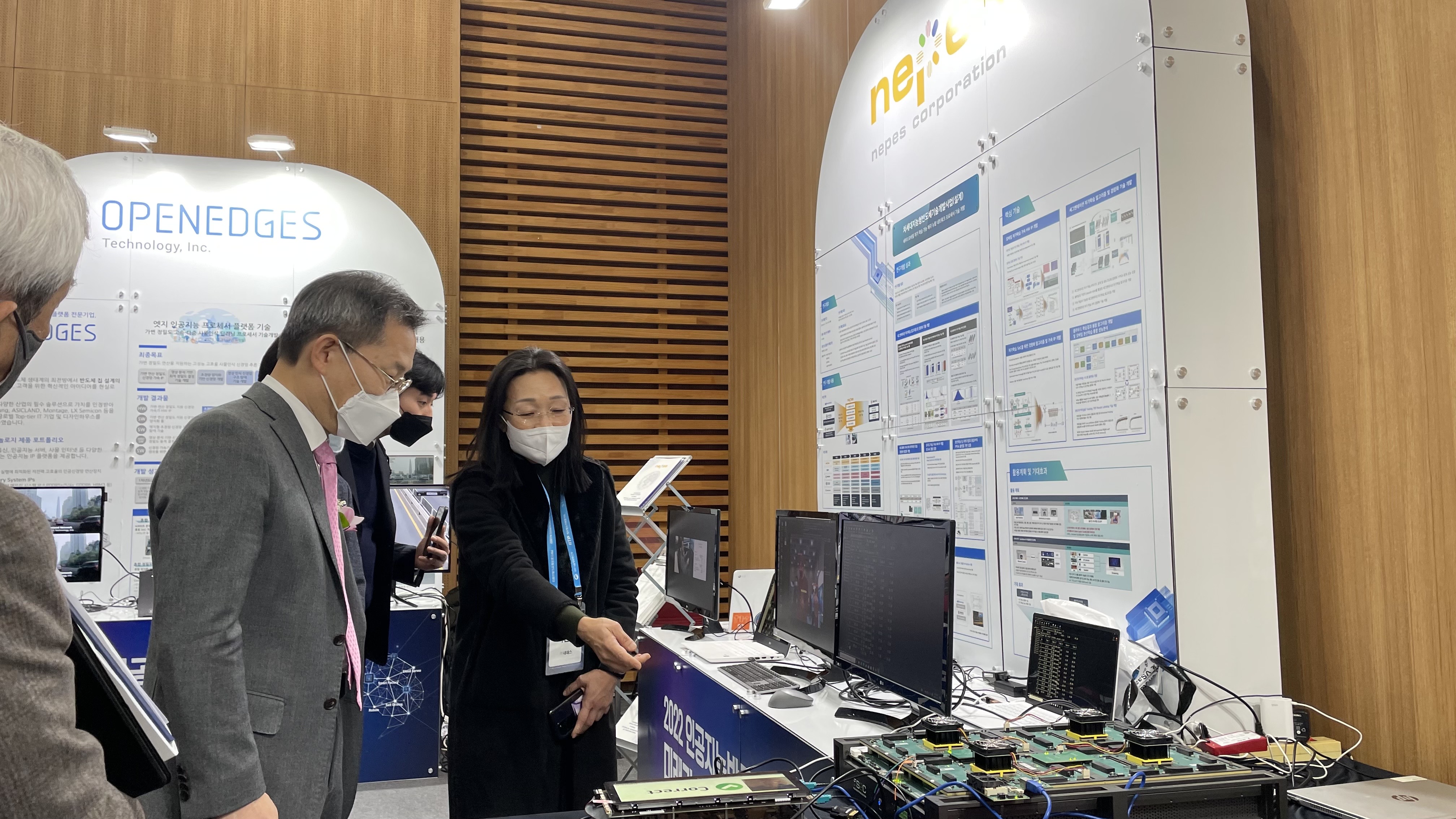

네패스, ISMP 2025에서 차세대 AI 반도체 패키징 기술 발표

네패스, ISMP 2025에서 차세대 AI 반도체 패키징 기술 발표네패스가 지난 11월 4일부터 7일까지 대구 인터불고 호텔에서 열린 ‘ISMP 2025(제23회 국제 마이크로전자 및 패키징 심포지엄)’에서, ‘Fan-Out Embedded Bridge Interposer for Scalable Heterogeneous Integration of NPUs and HBMs’를 주제로 발표를 성공적으로 마쳤다.이번 발표는 AI 및 고대역폭 메모리(HBM) 기반의 이기종 집적 기술을 위한 팬아웃 기반 브릿지 인터포저 개발 성과를 공유하는 자리로, 참석자들로부터 고밀도·고속·저전력 패키징 구현에 대한 실질적 해법을 제시했다는 평가를 받았다. ISMP 2025는 3D/2.5D Integration, Chiplet 기반 설계, Hybrid Bonding, UCIe 인터페이스 등 첨단 패키징 기술이 집중 조명된 국제 심포지엄으로, 올해는 특히 AI 반도체와 차세대 메모리 집적 기술에 대한 발표가 다수 이어졌다. 이번 심포지엄에는 인텔(Intel), 삼성전자, SK하이닉스, 램리서치(Lam Research), 도쿄일렉트론(Tokyo Electron), 펄스포지(PulseForge), 삼성전기 등 글로벌 반도체 선도 기업들이 발표자로 참여했으며, UCLA, USC, KAIST 등 주요 학계 인사들도 함께해 기술 교류와 협업 논의가 활발히 이루어졌다.네패스는 이번 발표를 통해 자체 개발한 Fan-Out Embedded Bridge Interposer 기술이 설계 유연성에서 우위를 가진다는 점을 강조했으며, AI 서버, 엣지 컴퓨팅, 자율주행차 등 고성능 응용 분야에서의 적용 가능성을 제시했다.이 날 발표를 맡은 반도체 연구소 이정원 소장은 “이번 ISMP 2025 발표는 현재 네패스가 진행하고있는 RDLinterposer 뿐 아니라 Fan-Out Embedded Bridge Interposer 기술 확보를 위해 노력하는 것을 보여주는 기회였다”며 “앞으로도 AI 반도체 패키징 분야에서 국내기업을 대표하여 기술 혁신을 지속해 나갈 것”이라고 전했다.[보도자료 배포 리스트 추가 요청]

2025-11-11 -

네패스, 대한민국 코칭컨페스티벌 2025 우수기관상 수상

네패스, 대한민국 코칭컨페스티벌 2025 우수기관상 수상사람 중심 조직문화 혁신 실천… 제조 현장에 확산된 코칭문화로 주목네패스는 지난 10월 31일, 서울 코엑스에서 열린 ‘제22회 대한민국 코칭컨페스티벌’에서 ‘2025 대한민국 코칭문화확산 우수기관상’을 수상했다. 이 상은 (사)한국코치협회가 매년 코칭 기반 조직문화 확산에 기여한 기관을 선정해 수여하는 것으로, 네패스는 사람중심경영 철학과 GRACE 모델을 기반으로 코칭리더십을 실천해온 점에서 높은 평가를 받았다. 특히, 네패스는 충북 청주에 위치한 중견기업으로서, 현장 중심의 교육 운영을 통해 산업 내 코칭 문화를 확산하는 실행력을 보여주며 주목받았다. 2024년 12월부터 1년간 전 임직원의 10% 이상이 참여하는 코칭교육을 현장에서 직접 운영 중이며, 현재까지 130명이 수료했고, 연말까지는 160명 이상이 이수할 것으로 예상된다. 이 중 19명이 KAC 자격을 취득, 2명은 KPC 자격을 보유하고 있어, 단순 교육을 넘어 공식 자격 인증을 통한 코칭리더십 내재화를 실천하고 있다. 또한, 네패스는 전문 코치들과 협업해 ‘코치 더 코치(Coach the Coach)’ 프로그램을 운영, 지방 산업 현장에서 자립적인 코칭 생태계를 조성하고 있다. 2024~2025년 동안 총 60명이 참여했으며, 22명의 전문 코치와 협업하여 200회 이상에 걸친 코칭 세션을 진행하며, 코칭이 일상 업무 속에서 실천되는 문화를 만들어가고 있다. 네패스의 조직문화는 GRACE 모델(Growth, Respect, Assistance, Conditions, Empathy)을 기반으로 설계되어 있으며, 특히 Empathy(마음챙김) 요소를 중심으로 공감조직 구성원 전원이 KAC 자격을 취득하도록 지원함으로써, 심리적 안전과 깊이 있는 소통을 실현하고 있다. 이들은 구성원의 상담, 경청, 케어를 전담하며, 사람 중심 경영 철학을 조직 내에 실질적으로 구현하고 있다. 이러한 코칭문화 확산 노력은 조직몰입도와 리더십 역량 향상이 수치로도 입증되고 있다. 예를 들어, ‘의사소통’ 항목은 2023년 4.41점에서 2024년 4.75점으로, ‘상사리더십’은 5.31점에서 5.56점으로 상승했으며, ‘코칭피드백’ 항목도 지속적으로 개선되고 있다.행사에서는 KAIST 김대식 교수의 기조강연과 하버드 의대 부속 코칭연구소 Carlos Davidovich 박사의 특별강연이 이어졌으며, 교육·HR·청소년·라이프 등 다양한 분야의 코칭 사례가 공유되었다. 네패스는 기술 중심 산업에서도 사람의 성장과 연결을 중시하는 기업 철학을 실천하며, 코칭을 통한 지속가능한 조직 성장 모델을 제시했다.대표 수상자인 네패스 이상호 경영지원실장은 "AI 시대에도 사람을 중심에 둔 조직문화가 경쟁력의 핵심”이라며 “이번 수상은 사람을 존중하는 네패스의 철학이 외부에서도 인정받은 결과”라고 밝혔다.한편, 올해 코칭문화확산 우수기관으로는 네패스를 포함해 HD현대그룹, KT cloud, 카카오뱅크, 한화에어로스페이스 등 총 21개 기관이 선정되었다.[보도자료 배포 리스트 추가 요청]

2025-11-11 -

함께 걸어온 35년, 함께 도약할 100년… 네패스 미래 경영 선언

함께 걸어온 35년, 함께 도약할 100년… 네패스 미래 경영 선언네패스는 창립 35주년을 맞아 청주2캠퍼스 아트리움에서 임직원과 함께하는 기념행사를 개최하고, 지난 35년의 여정을 돌아보며 향후 100년을 향한 경영 철학과 비전을 공유했다.이병구 회장은 이날 행사에서 “함께 걸어온 35년, 함께 걸어갈 100년”이라는 주제로 창립기념 메시지를 전하며, ▲사명 중심 성장 ▲영적 경영으로 비전 달성 ▲집단 지성으로 경쟁력 강화라는 미래 경영의 3가지 원칙을 제시했다.이 회장은 '네패스는 지난 35년간 끊임없는 혁신과 도전을 통해 반도체 산업 중심으로 국내 고객의 필요 기술을 개발하고 생산하며, 적기에 공급하는데 충실함으로 고객과 함께 괄목할 성장을 이루어 왔다.'며, '이는 고객 중심의 가치 실현을 통해 성장해 온 결과'라고 전했다. 앞으로도 수평적 소통, 합력과 협업, 다양성을 존중하는 문화, 실패를 두려워하지 않는 정신을 통해 함께 의논하고, 함께 결정하고 함께 책임지는 문화가 네패스를 100년 기업으로 이끄는 힘이 될 것이라고 강조했다.한편, 네패스는 이번 행사를 통해 공동체 정신과 AI 중심 전략 실행을 결합한 미래 경영의 실천적 기반을 다졌으며, ‘All hands on the AI Core’라는 2026년 슬로건 아래 임직원 모두가 미래 산업 환경에 선도적으로 대응해 나간다는 방침이다.[보도자료 배포 리스트 추가 요청]

2025-10-24 -

네패스, ‘반도체 패키징 발전 정책 포럼’서 중견 OSAT 기업의 성장 전략 제언

네패스, ‘반도체 패키징 발전 정책 포럼’서 중견 OSAT 기업의 성장 전략 제언네패스는 9월 25일 서울 SC컨벤션센터에서 열린 ‘반도체 패키징 발전 정책 포럼’에 CTO 김종헌 부사장이 연사로 참여해, ‘중견 OSAT기업의 성장 전략 및 산학연 협력 방안’을 주제로 발표했다.김 부사장은 발표에서, AI 반도체 시장의 핵심 기술인 2.5D 패키징(CoWoS)의 한계를 짚으며, “향후에는 고가 실리콘 인터포저를 대체하고 사각 패널 기반으로 전환하는 패키징 기술이 주목받을 것”이라고 전망했다. 이어 “업계에서는 수직 적층을 추가한 3.5D 패키징 기술까지 논의되고 있으며, 차세대 기술을 선점하고 공급망을 갖춘 기업이 시장 주도권을 확보할 것”이라고 강조했다.이와 함께, 김 부사장은 중견 OSAT 기업의 경쟁력 강화를 위한 전략적 방향성으로 △고객 맞춤형 기술 개발 △공급망 선제 구축 △차세대 패키징 기술 대응을 제시했다. 아울러 김 부사장은 중견 OSAT 기업의 기술 경쟁력 확보를 위해 정부의 정책적 지원과 투자 확대가 필요하다고 강조했다. 특히 첨단 패키징 기술의 상용화와 소재·장비 평가 인프라 구축을 위해서는 공공 부문의 역할이 중요하다는 점을 짚었다.이번 포럼은 한국마이크로전자 및 패키징학회(KMEPS)가 주관하고, 산업계·학계·연구기관 전문가들이 참여해 첨단 패키징 산업의 미래와 정책적 대응 방향을 논의하는 자리였다. 네패스는 이번 발표를 통해 중견 OSAT 기업의 기술 경쟁력 강화와 생태계 협력 전략에 대한 실질적 제언을 제시하며, 산업 내 리더십을 다시 한 번 입증했다.연관기사: [패키징 발전 정책 포럼]산업계 “패러다임 대전환…기술·시장 대응 전략도 바꿔야” - 전자신문

2025-09-26

IR

GLOBAL TOP-TIER PARTNER, NEPES

![[보도]소부장 핵심기업 '네패스' 국내 복귀…공급망 퍼즐 맞춘다 -산업부 정책뉴스 이미지1](https://www.nepes.co.kr/data/bbsData/17560881619.jpg)

![[보도]네패스, 첨단 패키징 기술로 보급형 엣지 컴퓨팅 시장 공략 - 시사저널e 이미지1](https://www.nepes.co.kr/data/bbsData/17442476949.jpg)

![[보도]청주시-㈜네패스, 고성능 첨단 반도체 생산시설 증설 투자협약 체결 이미지1](https://www.nepes.co.kr/data/bbsData/17433868169.jpg)

![[보도]네패스 코코아팹, `24년도 디지털새싹`사업 성료 및 우수 프로그램 선정 이미지1](https://www.nepes.co.kr/data/bbsData/17405324919.jpg)

![[보도]네패스 디지털 교육 활성화 기여, 2년 연속 교육부 장관 표창 수상 - 디지털타임즈 이미지1](https://www.nepes.co.kr/data/bbsData/17368230239.jpg)

![[DIC2024] 김종헌 네패스 “FO 패키징 ‘생산증가 원가절감’…韓 디자인-패키징 공급망 강화해야” 이미지1](https://www.nepes.co.kr/data/bbsData/17461609899.jpg)

![[뉴스]네패스, ISMP 2024 참가 이미지1](https://www.nepes.co.kr/data/bbsData/17307866199.png)

![[보도]네패스 "2.5D 첨단 패키징으로 AI 반도체 시장 공략" 이미지1](https://www.nepes.co.kr/data/bbsData/17243815749.jpg)

![[보도]네패스, AI 시대 겨냥 고성능 패키지 기술 개발 이미지1](https://www.nepes.co.kr/data/bbsData/17138335509.jpg)

![[보도][인터뷰] “패키지 핵심 기술로 AI 반도체 시장 공략” 이미지1](https://www.nepes.co.kr/data/bbsData/17133309399.jpg)

![[보도]네패스, 지멘스EDA 솔루션으로 3D 패키징 이미지1](https://www.nepes.co.kr/data/bbsData/17098738449.png)

![[보도]네패스 디지털 교육 활성화 기여, 교육부 장관 표창 수상 이미지1](https://www.nepes.co.kr/data/bbsData/17036449079.jpg)

![[보도]이스라엘 AI아버지·K반도체 전격 의기투합 이미지1](https://www.nepes.co.kr/data/bbsData/16805747669.jpg)

![[테크코리아 우리가 이끈다]네패스 - 전자신문 이미지1](https://www.nepes.co.kr/data/bbsData/16635505429.jpg)

![[반도체 패키징데이 2022]네패스, FO-PLP 적용 영역 확대 - 전자신문 이미지1](https://www.nepes.co.kr/data/bbsData/16571787239.jpeg)

![[보도자료]네패스, 미국 반도체 혁신 연합(ASIC) 가입… 글로벌 반도체 협력 강화 이미지1](https://www.nepes.co.kr/data/bbsData/16557778409.jpg)

![[보도] ㈜네패스, 폴리텍대 청주캠에 반도제 훈련 장비 기증 -충청일보 이미지1](https://www.nepes.co.kr/data/bbsData/16541327949.jpg)

![[보도]반도체 업계 “미세공정 한계, 패키징 기술 대안” 이미지1](https://www.nepes.co.kr/data/bbsData/16539562229.jpg)

![[보도]괴산군 청안면주민자치위원회, ㈜네패스아크와 자매결연 협약 이미지1](https://www.nepes.co.kr/data/bbsData/16530083659.jpg)

![[보도]반도체 지네발 없앴던 네패스 “반도체 패키징 효율 10배…3년 내 매출 1조원 달성” 이미지1](https://www.nepes.co.kr/data/bbsData/16505874909.jpg)

![[보도]이병구 네패스 회장 "반도체, 사각형으로 패키징…생산성 10배 높여" 이미지1](https://www.nepes.co.kr/data/bbsData/16505873269.jpg)

![[보도]우리 지역 글로벌 기업/2. 첨단 파운드리 인프라 확장해가는 (주)네패스 이미지1](https://www.nepes.co.kr/data/bbsData/16466976519.jpg)

![[보도]반도체 투자 활성화를 위한 기업 간담회 개최 이미지1](https://www.nepes.co.kr/data/bbsData/16450737419.jpg)

![[보도][Issue&Biz] 인공지능·빅데이터 도입…반도체공정 혁신 씨앗 심었다 이미지1](https://www.nepes.co.kr/data/bbsData/16408506559.jpg)

![[보도]충북대, 네패스의 반도체 및 IT 분야 인력 양성에 앞장 이미지1](https://www.nepes.co.kr/data/bbsData/16406768519.jpg)

![[보도]백악관도 극찬한 韓 반도체 기업…서로 존중하는 ‘슈퍼스타 경영’의 힘 이미지1](https://www.nepes.co.kr/data/bbsData/16403127989.jpg)

![[보도][제58회 무역의 날] 2억불 탑 (주)네패스 이미지1](https://www.nepes.co.kr/data/bbsData/16387707239.jpg)

![[보도][지역특화 스마트IT산업, AI융합엔진 장착] 반도체패키징·태양광 전문기업 데이터 경영 활성화 이미지1](https://www.nepes.co.kr/data/bbsData/16376595039.jpg)

![[보도][2021 독서경영 우수직장-최우수상]네패스 이미지1](https://www.nepes.co.kr/data/bbsData/16360020649.jpg)

![[보도] 반도체 패키징 첨단기술, 백악관도 찍었다 이미지1](https://www.nepes.co.kr/data/bbsData/16336551869.jpg)

![[보도]네패스, 차세대 패키징 'FO-PLP' 양산 개시…PMIC '세계 최초' 이미지1](https://www.nepes.co.kr/data/bbsData/16333950019.jpg)

![[보도] 네패스, 전통적인 웨이퍼 레벨 패키징서 한걸음 진보 이미지1](https://www.nepes.co.kr/data/bbsData/16330486029.jpg)

![[보도]반도체 초강국 이끌 '최상위 협의체' 출범 이미지1](https://www.nepes.co.kr/data/bbsData/16328146139.jpg)

![[보도]'1000억 투자' 네패스그룹, 삼성전자 협업 강화 '시그널' 이미지1](https://www.nepes.co.kr/data/bbsData/16318463439.jpg)

![[보도] [글로벌테크코리아 2021] 김종헌 네패스 CTO "차세대 패키징 기술 상용화 박차" 이미지1](https://www.nepes.co.kr/data/bbsData/16310576999.jpg)

![[보도] “네패스, 반도체 후공정인 패키징 및 테스트 기술력 보유” -뉴스투데이 이미지1](https://www.nepes.co.kr/data/bbsData/16291595169.jpg)

![[보도]첨단 반도체 패키징 기술 무장 '네패스' -전자신문 이미지1](https://www.nepes.co.kr/data/bbsData/16276038749.jpg)

![[보도] “초소형-고성능 패키징 기술로…韓 반도체 판도 바꿀 것” - 동아일보 이미지1](https://www.nepes.co.kr/data/bbsData/16196720229.jpg)

![[보도]「基板なし」が主流に 기판 공급 부족 "대란" - 日 Daily NNA 이미지1](https://www.nepes.co.kr/data/bbsData/16196608579.png)

![[보도] 폴리텍 청주캠 - 네패스 맞춤형 인력양성 업무 협의-충청타임즈 이미지1](https://www.nepes.co.kr/data/bbsData/16194047609.jpg)

![[보도]Employee-centered management drives success-The Korea Times 이미지1](https://www.nepes.co.kr/data/bbsData/16184755729.jpg)

![[보도]네패스, 반도체 총괄 회장에 정칠희 삼성전자 고문 영입 이미지1](https://www.nepes.co.kr/data/bbsData/16152477089.jpg)

![[보도]이병구 네패스 회장 "동서고금 기업 경영의 핵심은 '사람의 마음'이죠"-한국경제 이미지1](https://www.nepes.co.kr/data/bbsData/16121410139.jpg)

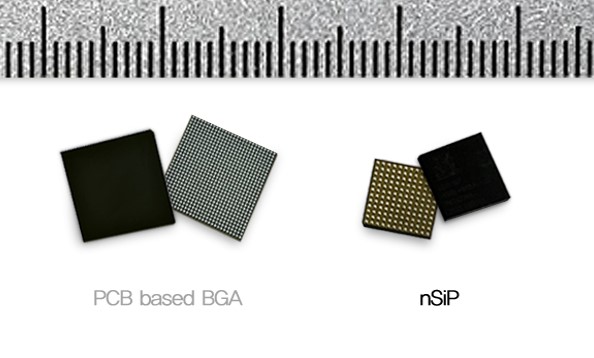

![[보도]네패스, '시스템인패키지(SiP)' 신기술 공개 -한국경제 이미지1](https://www.nepes.co.kr/data/bbsData/16118772609.jpg)

![[보도]High-tech parts suppliers to watch in 2021-The Korea Times 이미지1](https://www.nepes.co.kr/data/bbsData/16099940859.jpg)

![[보도]新기술에 굶주린 반도체 패키징 강자…적자 때도 2000억 투자 -한국경제 이미지1](https://www.nepes.co.kr/data/bbsData/16098368659.jpg)

![[보도]고급 패키징 수요 급증…年 평균 13% 성장 -한국경제 이미지1](https://www.nepes.co.kr/data/bbsData/16100019849.jpg)

![[보도] 뉴로모픽칩 하이엔드 CCTV 많이 채용-전파신문 이미지1](https://www.nepes.co.kr/data/bbsData/16052562179.jpg)

![[보도]'테스트 전문가' 네패스아크, 韓 시스템반도체 성장 이끈다 이미지1](https://www.nepes.co.kr/data/bbsData/16052561219.jpg)

![[보도]한동대, 네패스와 반도체 및 AI산학 협력 협약 이미지1](https://www.nepes.co.kr/data/bbsData/16052551689.jpg)