'앤드 팹 파운드리' 솔루션 발판으로

글로벌 시장 적극 진출

생산성 높은 패널레벨패키지(PLP) 적용 성공

'nSiP' 등 차별화된 기술력 앞세워 고객 확보

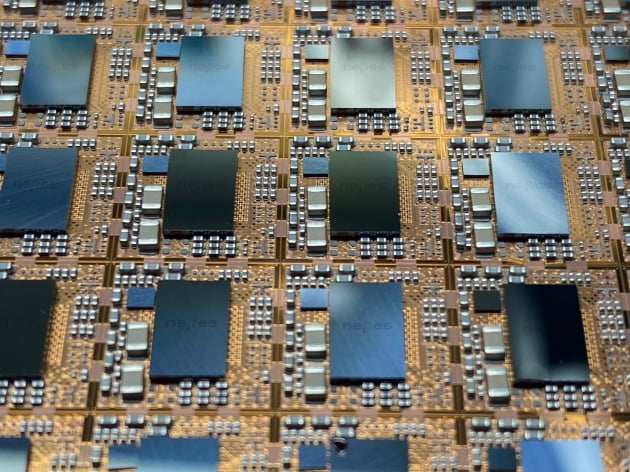

네패스가 독자 기술로 구현한 nSiP 모습. 기존 PCB기반 SiP 대비 초소형, 경량화가 가능하다. 네패스 제공

네패스는 "지난 27일 온라인 포럼을 열고 웨이퍼레벨패키지(WLP), 팬아웃패키지(FOWLP)·PLP, SiP로 이어지는 ‘엔드-팹 파운드리’(반도체 후공정) 솔루션 로드맵을 공개했다"고 28일 발표했다.

SiP는 개별 칩들을 하나로 묶는 패키징 솔루션이다. 스마트폰 주요 부품 중 73%가 SiP로 구성돼있다. 현재 활용되는 SiP의 90% 이상이 서브스트레이트(substrate)나 와이어(wire) 같은 부품을 적용한 전통적인 방식이다.

네패스는 기판을 사용하는 전통적인 방식 대신 실리콘 웨이퍼에 직접 패키징을 하는 FOWLP기술을 갖고 있다. 이를 발판으로 ‘nSiP’라 불리는 고유 기술을 개발했다. 기판과 와이어를 이용한 방식과 비교해 패키지 면적을 '3분의 1' 이하로 작게 만들 수 있다. 네패스는 가로·세로 600mm 사각 패널을 이용해 생산 효율성을 극대화한 PLP(패널레벨패키지)공정으로 가격 경쟁력까지 확보했다. 네패스 관계자는 "SiP 시장의 게임체인저가 될 것"이라고 전망했다.

시장조사업체 욜(Yole)에 따르면 지난해 SiP 시장 규모는 146억달러다. 오는 2025년까지 188억 달러 규모로 성장할 전망이다. 연 평균 성장률은 약 6%다. 김종헌 네패스 CTO실 전무는 "엔드팹 기반의 nSiP 는 크기와 성능에서 세계적인 경쟁력을 확보했다"며 "이 기술을 PLP 상에서 구현해 시장에 새로운 SiP 로드맵을 제시할 것"이라고 설명했다.

-하략-

[원문보기 = 한국경제 https://www.hankyung.com/economy/article/202101283854i]