테스트부터 패키징까지

반도체 후공정 턴키 제공

첨단 기술로 칩 성능 개선

![[상장기업 분석] 첨단 반도체 패키징 기술 무장 '네패스'](https://img.etnews.com/photonews/2107/1439234_20210729162619_388_0007.jpg)

네패스는 우리나라의 대표 반도체 후공정(OSAT) 기업이다. 반도체 제조는 웨이퍼에 회로 패턴을 그려 반도체 다이를 만드는 전공정과 다이를 테스트하고 패키징해 칩으로 만드는 후공정으로 나뉜다. 전공정은 초미세 공정으로 전환이 점점 어려워지고 있다. 반도체 칩 성능을 끌어올리기 위한 후공정이 주목받는 배경이다. 네패스는 테스트부터 패키징까지 후공정의 거의 모든 과정을 '턴키'로 제공한다.

2000년 회사 내 반도체사업부를 신설하고 2001년 당시 150억원을 투자해 충북 오창에 부지 3000평 규모 패키징(플립침용 범프) 생산라인을 구축했다. 20년이 지난 지금 네패스의 반도체 부문은 계열사 포함 전체 매출의 83%를 차지할 정도로 핵심 사업으로 부상했다.

네패스는 끊임없는 연구개발(R&D)과 인프라 투자로 패키징 기술을 선도하는 기업이 됐다. 특히 팬아웃(FO) 분야에 압도적 우위를 자랑한다. 팬아웃은 반도체 다이 밖까지 재배선층(RDL)을 확장시켜 반도체 칩의 신호 입출력(I/O)을 늘리는 기술이다. 전력 효율성을 크게 높이고 칩의 신호 처리 능력도 개선할 수 있다. TSMC가 삼성으로부터 애플 칩 생산을 가져올 수 있었던 것도 이 팬아웃 기술 때문으로 알려졌다.

네패스의 팬아웃 패키징은 자회사인 네패스라웨와 네패스하임이 담당한다. 네패스는 팬아웃 패키징에 힘을 싣기 위해 2020년 2월 네패스라웨를 물적 분할했다.

![[상장기업 분석] 첨단 반도체 패키징 기술 무장 '네패스'](https://img.etnews.com/photonews/2107/1439234_20210729162619_388_0006.jpg)

■강점과 기회

네패스 강점은 첨단 팬아웃 패키징 기술에 있다. 팬아웃웨이퍼레벨패키징(FO-WLP)과 팬아웃패널레벨패키징(FO-PLP)이다.

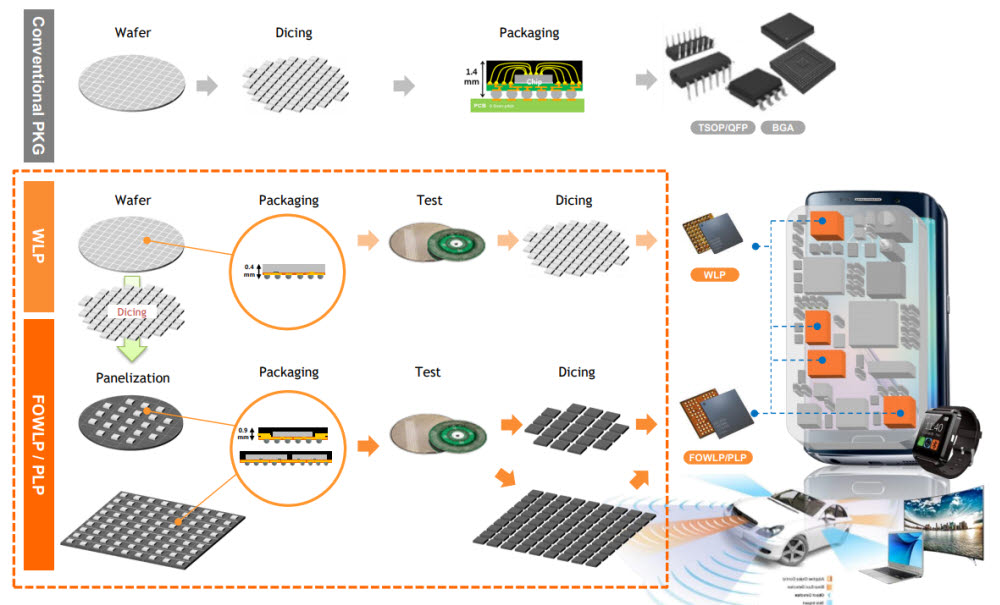

전통적인 패키징은 웨이퍼에 회로를 그려 반도체 다이를 만든 후(전공정), 웨이퍼를 개별 다이로 자른다. 이를 다시 패키징 기판에 범핑해 연결하는 방식이다. 공정 과정이 여러 단계고 패키징 기판이 필요해 시간과 비용이 많이 들었다.

이런 제약을 극복하기 위한 것이 웨이퍼레벨패키징(WLP)이다. WLP는 웨이퍼에 바로 RDL를 형성해 공정 과정을 줄인다. 또 웨이퍼에서 바로 패키징하기 때문에 패키징 기판을 사용하지 않는다. 비용 절감 효과뿐만 아니라 칩을 가볍고 얇게 만들 수 있다. 네패스에서 물적 분할한 네패스라웨가 글로벌 전장부품 업체에 FO-WLP을 제공하고 있다.

네패스는 한발 더 나아가 FO-PLP까지 상용화했다. PLP는 웨이퍼에 직접 패키징하는 WLP와 달리 반도체 다이를 사각형 패널에 배치해 패키징하는 기술이다. 원형에서 패키징하는 것보다 생산성은 높이고 비용을 줄일 수 있다. 네패스는 가로, 세로 각각 600mm 크기 사각 패널을 사용하는데 300mm(12인치) 웨이퍼 대비 장당 5~6배 많은 반도체를 생산할 수 있다. 보통 PLP는 WLP 방식보다 생산성이 96% 높은 것으로 알려졌다.

세계에서 FO-PLP 기술을 가진 회사는 네패스와 삼성전자, ASE, 파워텍, JCET 등이 있다. 네패스는 FO-PLP 패키징 설비 등 인프라 구축에 2019년 말부터 2000억원 이상을 투자했다. 충북 괴산군 청안에 약 6만평 규모 패키징 공장을 세웠다. 현재 양산 준비 단계로 알려졌다. 글로벌 팹리스 업체의 전력관리반도체(PMIC) 패키징에 FO-PLP를 적용하기 위한 성능 테스트를 진행 중이다. 최종 양산 승인을 받으면 PMIC에 FO-PLP를 적용한 세계 첫 사례가 될 전망이다. 이르면 하반기부터 매출이 발생할 가능성이 크다.

네패스 패키징 매출 가운데 PMIC와 디스플레이구동칩(DDI)가 절반이다. PMIC는 네패스의 주력이기도 하다. 국내 주요 고객사의 PMIC를 패키징, 테스트하고 있다. 최근 정보기술(IT) 기기가 고사양화하면서 효율적인 전력 관리를 위한 PMIC 채택이 늘고 있다. 스마트폰에서 PMIC 침투율이 높은데, 롱텀에벌루션(LTE) 스마트폰 대비 5세대(5G) 이동통신 스마트폰에서 PMIC가 2~3개 더 많이 쓰일 것으로 전망된다. 5G 스마트폰 시장이 크게 성장하고 있어 네패스 패키징 사업에는 호재다.

네패스 계열사 간 시너지 확대가 용이하다는 것도 또 다른 강점이다. 네패스라웨과 2020년 11월 상장한 네패스아크가 대표적이다. 네패스가 주력으로 하는 시스템반도체는 메모리보다 다품종 소량 생산 방식이며 기술 난도가 높아 후공정 생태계 분업화가 필요하다. 네패스는 WLP, 네패스라웨는 팬아웃, 네패스아크가 테스트를 맡으며 고객사가 요구하는 '원스톱' 후공정 서비스를 제공할 수 있다.

-하략-

권동준기자 djkwon@etnews.com

[원문보기 = 전자신문 https://www.etnews.com/20210729000082]